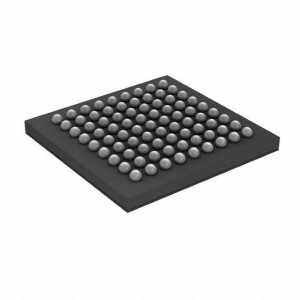

TMS320VC5509AZAY ตัวประมวลผลและตัวควบคุมสัญญาณดิจิทัล – ตัวประมวลผลสัญญาณดิจิทัล DSP, DSC Fixed-Point 179-NFBGA -40 ถึง 85

♠รายละเอียดสินค้า

| คุณลักษณะของผลิตภัณฑ์ | ค่าแอตทริบิวต์ |

| ผู้ผลิต: | เท็กซัส อินสตรูเมนท์ |

| ประเภทสินค้า: | ตัวประมวลผลและตัวควบคุมสัญญาณดิจิทัล - DSP, DSC |

| เป็นไปตามมาตรฐาน: | รายละเอียด |

| ผลิตภัณฑ์: | DSP |

| ชุด: | TMS320VC5509A |

| สไตล์การติดตั้ง: | เอสเอ็มดี/SMT |

| แพ็คเกจ/กล่อง: | NFBGA-179 |

| หลัก: | C55x |

| จำนวนแกน: | 1 แกน |

| ความถี่นาฬิกาสูงสุด: | 200 เมกะเฮิรตซ์ |

| หน่วยความจำคำสั่งแคช L1: | - |

| หน่วยความจำข้อมูลแคช L1: | - |

| ขนาดหน่วยความจำโปรแกรม: | 64 กิโลไบต์ |

| ขนาด RAM ข้อมูล: | 256 กิโลไบต์ |

| แรงดันไฟฟ้าในการทำงาน: | 1.6 โวลต์ |

| อุณหภูมิในการทำงานต่ำสุด: | - 40 องศาเซลเซียส |

| อุณหภูมิในการทำงานสูงสุด: | + 85 องศาเซลเซียส |

| บรรจุภัณฑ์: | ถาด |

| ยี่ห้อ: | เท็กซัส อินสตรูเมนท์ |

| ประเภทคำสั่ง: | จุดคงที่ |

| ประเภทอินเทอร์เฟซ: | ไอทูซี |

| ไวต่อความชื้น: | ใช่ |

| ประเภทสินค้า: | DSP - ตัวประมวลผลและตัวควบคุมสัญญาณดิจิทัล |

| ปริมาณแพ็คโรงงาน: | 160 |

| หมวดหมู่ย่อย: | โปรเซสเซอร์และคอนโทรลเลอร์แบบฝังตัว |

| แรงดันไฟ - สูงสุด: | 1.65 โวลต์ |

| การจ่ายแรงดัน - ต่ำสุด: | 1.55 โวลต์ |

| ตัวจับเวลา Watchdog: | วอชด็อก ไทม์เมอร์ |

♠ TMS320VC5509A โปรเซสเซอร์สัญญาณดิจิตอลแบบ Fixed-Point

ตัวประมวลผลสัญญาณดิจิตอลจุดคงที่ (DSP) TMS320VC5509A ใช้แกนประมวลผล CPU รุ่น TMS320C55x DSPสถาปัตยกรรม C55x™ DSP ให้ประสิทธิภาพสูงและใช้พลังงานต่ำผ่านการทำงานแบบคู่ขนานที่เพิ่มขึ้นและมุ่งเน้นที่การลดการกระจายพลังงานทั้งหมดCPU รองรับโครงสร้างบัสภายในที่ประกอบด้วยบัสโปรแกรมหนึ่งบัส บัสอ่านข้อมูลสามบัส บัสเขียนข้อมูลสองบัส และบัสเพิ่มเติมสำหรับกิจกรรมต่อพ่วงและ DMA โดยเฉพาะบัสเหล่านี้ให้ความสามารถในการอ่านข้อมูลได้สูงสุดสามครั้งและเขียนข้อมูลได้สองครั้งในรอบเดียวในขณะเดียวกัน ตัวควบคุม DMA สามารถทำการถ่ายโอนข้อมูลได้สูงสุดสองครั้งต่อรอบโดยไม่ขึ้นกับกิจกรรมของ CPU

CPU C55x มีหน่วยคูณสะสม (MAC) สองหน่วย แต่ละหน่วยสามารถคูณ 17 บิต x 17 บิตในรอบเดียวหน่วยเลขคณิต/ลอจิกกลาง 40 บิต (ALU) ได้รับการสนับสนุนโดย ALU 16 บิตเพิ่มเติมการใช้ ALU อยู่ภายใต้การควบคุมชุดคำสั่ง ทำให้สามารถเพิ่มประสิทธิภาพกิจกรรมคู่ขนานและการใช้พลังงานทรัพยากรเหล่านี้ได้รับการจัดการใน Address Unit (AU) และ Data Unit (DU) ของ C55x CPU

รุ่น C55x DSP รองรับชุดคำสั่งความกว้างของไบต์แบบแปรผันเพื่อปรับปรุงความหนาแน่นของโค้ดInstruction Unit (IU) ทำการดึงโปรแกรม 32 บิตจากหน่วยความจำภายในหรือภายนอก และจัดคิวคำสั่งสำหรับ Program Unit (PU)หน่วยโปรแกรมถอดรหัสคำสั่ง ส่งงานไปยังทรัพยากร AU และ DU และจัดการไปป์ไลน์ที่ได้รับการป้องกันอย่างเต็มที่ความสามารถในการแยกสาขาแบบคาดการณ์หลีกเลี่ยงการล้างไปป์ไลน์เมื่อดำเนินการตามคำสั่งแบบมีเงื่อนไข

ฟังก์ชันอินพุตและเอาต์พุตที่ใช้งานทั่วไปและ A/D แบบ 10 บิตมีพินเพียงพอสำหรับสถานะ การขัดจังหวะ และบิต I/O สำหรับ LCD แป้นพิมพ์ และอินเทอร์เฟซมีเดียอินเทอร์เฟซแบบขนานทำงานในสองโหมด ไม่ว่าจะเป็นแบบทาสของไมโครคอนโทรลเลอร์โดยใช้พอร์ต HPI หรือเป็นอินเทอร์เฟซสื่อแบบขนานโดยใช้ EMIF แบบอะซิงโครนัสรองรับสื่อแบบอนุกรมผ่านอุปกรณ์ต่อพ่วง MultiMedia Card/Secure Digital (MMC/SD) สองตัวและ McBSP สามตัว

ชุดอุปกรณ์ต่อพ่วง 5509A ประกอบด้วยอินเทอร์เฟซหน่วยความจำภายนอก (EMIF) ที่ให้การเข้าถึงหน่วยความจำแบบอะซิงโครนัส เช่น EPROM และ SRAM แบบไร้กาว ตลอดจนหน่วยความจำที่มีความเร็วสูงและมีความหนาแน่นสูง เช่น DRAM แบบซิงโครนัสอุปกรณ์ต่อพ่วงเพิ่มเติม ได้แก่ Universal Serial Bus (USB), นาฬิกาเรียลไทม์, ตัวจับเวลาจ้องจับผิด, I2C multi-master และ slave interfaceพอร์ตซีเรียลบัฟเฟอร์หลายช่องแบบฟูลดูเพล็กซ์สามพอร์ต (McBSPs) ให้อินเทอร์เฟซแบบไร้กาวกับอุปกรณ์ซีเรียลมาตรฐานอุตสาหกรรมที่หลากหลาย และการสื่อสารแบบหลายช่องด้วยช่องสัญญาณที่เปิดใช้งานแยกกันมากถึง 128 ช่องอินเทอร์เฟซพอร์ตโฮสต์ที่ปรับปรุงแล้ว (HPI) เป็นอินเทอร์เฟซแบบขนาน 16 บิตที่ใช้เพื่อให้ตัวประมวลผลโฮสต์เข้าถึงหน่วยความจำภายใน 32K ไบต์บน 5509Aสามารถกำหนดค่า HPI ในโหมดมัลติเพล็กซ์หรือโหมดไม่มัลติเพล็กซ์เพื่อให้อินเทอร์เฟซไร้กาวกับโปรเซสเซอร์โฮสต์ที่หลากหลายตัวควบคุม DMA จัดเตรียมการเคลื่อนย้ายข้อมูลสำหรับบริบทช่องสัญญาณอิสระ 6 ช่องโดยไม่มีการแทรกแซงของ CPU โดยให้ปริมาณงาน DMA สูงสุด 2 คำ 16 บิตต่อรอบมีตัวจับเวลาสำหรับใช้งานทั่วไป 2 ตัว พิน I/O (GPIO) สำหรับใช้งานทั่วไปโดยเฉพาะสูงสุด 8 ตัว และการสร้างสัญญาณนาฬิกา Digital Phase-locked Loop (DPLL) รวมอยู่ด้วย

5509A ได้รับการสนับสนุนโดย eXpressDSP™ ที่ได้รับรางวัลในอุตสาหกรรม, Code Composer Studio™ Integrated Development Environment (IDE), DSP/BIOS™, มาตรฐานอัลกอริทึมของ Texas Instruments และเครือข่ายบุคคลที่สามที่ใหญ่ที่สุดในอุตสาหกรรมCode Composer Studio IDE มีเครื่องมือสร้างโค้ด ได้แก่ C Compiler และ Visual Linker, โปรแกรมจำลอง, RTDX™, ไดรเวอร์อุปกรณ์จำลอง XDS510™ และโมดูลการประเมินผล5509A ยังรองรับโดย C55x DSP Library ซึ่งมีเคอร์เนลซอฟต์แวร์พื้นฐานมากกว่า 50 รายการ (ตัวกรอง FIR, ตัวกรอง IIR, FFT และฟังก์ชันทางคณิตศาสตร์ต่างๆ) รวมถึงไลบรารีที่สนับสนุนชิปและบอร์ด

แกน DSP TMS320C55x ถูกสร้างขึ้นด้วยสถาปัตยกรรมแบบเปิดที่อนุญาตให้เพิ่มฮาร์ดแวร์เฉพาะแอปพลิเคชันเพื่อเพิ่มประสิทธิภาพให้กับอัลกอริทึมเฉพาะส่วนขยายของฮาร์ดแวร์ใน 5509A สร้างความสมดุลที่สมบูรณ์แบบของประสิทธิภาพการทำงานแบบตายตัวกับความยืดหยุ่นในการเขียนโปรแกรม ในขณะที่ใช้พลังงานต่ำ และต้นทุนที่ปกติแล้วหาได้ยากในตลาดโปรเซสเซอร์วิดีโอส่วนขยายนี้ช่วยให้ 5509A สามารถนำเสนอประสิทธิภาพของตัวแปลงสัญญาณวิดีโอที่ยอดเยี่ยมโดยมีแบนด์วิธมากกว่าครึ่งหนึ่งสำหรับใช้งานฟังก์ชันเพิ่มเติม เช่น การแปลงพื้นที่สี การดำเนินการส่วนต่อประสานกับผู้ใช้ ความปลอดภัย TCP/IP การจดจำเสียง และการแปลงข้อความเป็นคำพูดด้วยเหตุนี้ 5509A DSP ตัวเดียวจึงสามารถจ่ายพลังงานให้กับแอปพลิเคชันวิดีโอดิจิทัลแบบพกพาส่วนใหญ่โดยมีพื้นที่เหลือในการประมวลผลเหลือเฟือสำหรับข้อมูลเพิ่มเติม โปรดดู TMS320C55x Hardware Extensions for Image/Video Applications Programmer's Reference (หมายเลขตามตัวอักษร SPRU098)สำหรับข้อมูลเพิ่มเติมเกี่ยวกับการใช้ DSP Image Processing Library โปรดดูที่ TMS320C55x Image/Video Processing Library Programmer's Reference (หมายเลขตามตัวอักษร SPRU037)

• ตัวประมวลผลสัญญาณดิจิตอล TMS320C55x™ ประสิทธิภาพสูง กำลังไฟต่ำ จุดคงที่

− 9.26-, 6.95-, 5-ns รอบเวลาการสอน

− อัตราสัญญาณนาฬิกา 108-, 144-, 200-MHz

- ดำเนินการหนึ่งหรือสองคำสั่งต่อรอบ

- ตัวคูณคู่ [มากถึง 400 ล้านคูณสะสมต่อวินาที (MMACS)]

− สองหน่วยเลขคณิต/ลอจิก (ALU)

− บัสข้อมูลภายใน/ตัวดำเนินการอ่าน 3 ตัว และบัสข้อมูลภายใน/ตัวดำเนินการเขียน 2 ตัว

• 128K x 16-Bit บนชิป RAM ประกอบด้วย:

− 64K Bytes ของ Dual-Access RAM (DARAM) 8 บล็อค 4K × 16-Bit

− 192K Bytes ของ Single-Access RAM (SARAM) 24 บล็อค 4K × 16-Bit

• 64K ไบต์ของ One-Wait-State On-Chip ROM (32K × 16-Bit)

• พื้นที่หน่วยความจำภายนอกที่สามารถระบุตำแหน่งได้สูงสุด 8M × 16 บิต (DRAM แบบซิงโครนัส)

• 16-Bit External Parallel Bus Memory รองรับอย่างใดอย่างหนึ่ง:

- อินเทอร์เฟซหน่วยความจำภายนอก (EMIF) พร้อมความสามารถ GPIO และอินเทอร์เฟซไร้กาว เพื่อ:

- RAM แบบคงที่แบบอะซิงโครนัส (SRAM)

- EPROM แบบอะซิงโครนัส

- DRAM แบบซิงโครนัส (SDRAM)

− 16-Bit Parallel Enhanced Host-Port Interface (EHPI) พร้อมความสามารถ GPIO

• การควบคุมพลังงานต่ำที่ตั้งโปรแกรมได้ของโดเมนการทำงานของอุปกรณ์หกตัว

• ลอจิกจำลองบนชิปสแกน

• อุปกรณ์ต่อพ่วงบนชิป

- ตัวจับเวลา 20 บิตสองตัว

- จับเวลาจ้องจับผิด

- คอนโทรลเลอร์ Direct Memory Access (DMA) หกช่องสัญญาณ

- พอร์ตอนุกรมสามพอร์ตที่รองรับการรวมกันของ:

- พอร์ตอนุกรมบัฟเฟอร์แบบหลายช่องสัญญาณ (McBSPs) สูงสุด 3 ช่อง

- อินเทอร์เฟซมัลติมีเดีย/การ์ดดิจิทัลที่ปลอดภัยสูงสุด 2 รายการ

- เครื่องกำเนิดสัญญาณนาฬิกาแบบล็อคเฟสที่ตั้งโปรแกรมได้

− เจ็ด (LQFP) หรือแปด (BGA) พินสำหรับใช้งานทั่วไป I/O (GPIO) และพินสำหรับใช้งานทั่วไป (XF)

- พอร์ตสเลฟความเร็วเต็ม USB (12 Mbps) รองรับการถ่ายโอนจำนวนมาก การขัดจังหวะ และ Isochronous

- Inter-Integrated Circuit (I2C) Multi-Master และ Slave Interface

−นาฬิกาเรียลไทม์ (RTC) พร้อมอินพุตคริสตัล, โดเมนนาฬิกาแยกต่างหาก, แหล่งจ่ายไฟแยกต่างหาก

− 4-Channel (BGA) หรือ 2-Channel (LQFP) 10-Bit ต่อเนื่องประมาณ A/D

• IEEE Std 1149.1† (JTAG) ลอจิกการสแกนขอบเขต

• แพ็คเกจ:

− 144-Terminal Low-Profile Quad Flatpack (LQFP) (ส่วนต่อท้าย PGE)

− 179-Terminal MicroStar BGA™ (อาร์เรย์บอลกริด) (ส่วนต่อท้าย GHH)

− 179-Terminal MicroStar BGA™ ไร้สารตะกั่ว (Ball Grid Array) (ZHH Suffix)

• 1.2-V คอร์ (108 MHz), 2.7-V – 3.6-VI/Os

• 1.35-V คอร์ (144 MHz), 2.7-V – 3.6-VI/Os

• 1.6-V คอร์ (200 MHz), 2.7-V – 3.6-VI/Os

• ระบบไฮบริด ระบบไฟฟ้า และพลังงานไฟฟ้า (EV/HEV)

– ระบบจัดการแบตเตอรี่ (BMS)

- ที่ชาร์จในตัว

- อินเวอร์เตอร์ฉุด

- ตัวแปลง DC/DC

- สตาร์ทเตอร์ / เครื่องกำเนิดไฟฟ้า