TMS320C6678ACYPA มัลติคอร์ Fix/Float Pt Dig Sig Proc

♠รายละเอียดสินค้า

| คุณลักษณะของผลิตภัณฑ์ | ค่าแอตทริบิวต์ |

| ผู้ผลิต: | เท็กซัส อินสตรูเมนท์ |

| ประเภทสินค้า: | ตัวประมวลผลและตัวควบคุมสัญญาณดิจิทัล - DSP, DSC |

| ผลิตภัณฑ์: | DSP |

| ชุด: | TMS320C6678 |

| สไตล์การติดตั้ง: | เอสเอ็มดี/SMT |

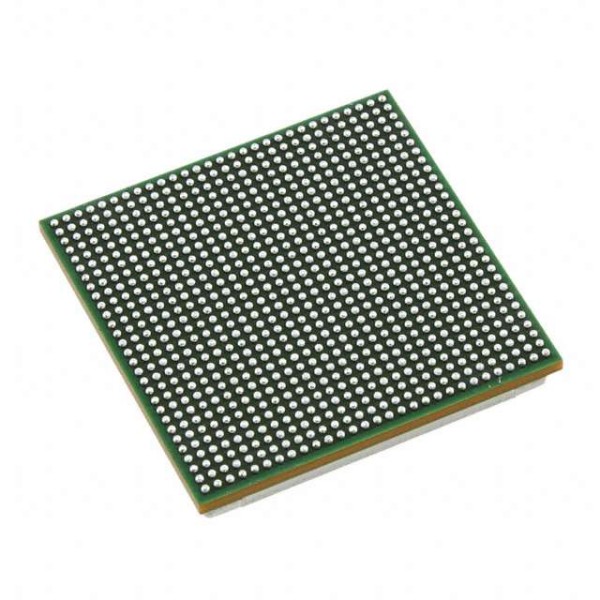

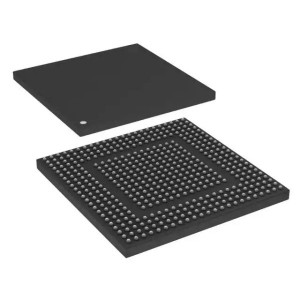

| บรรจุภัณฑ์ / กล่อง: | FCBGA-841 |

| หลัก: | C66x |

| จำนวนแกน: | 8 แกน |

| ความถี่นาฬิกาสูงสุด: | 1 กิกะเฮิรตซ์, 1.25 กิกะเฮิรตซ์ |

| หน่วยความจำคำสั่งแคช L1: | 8 x 32 กิโลไบต์ |

| หน่วยความจำข้อมูลแคช L1: | 8 x 32 กิโลไบต์ |

| ขนาดหน่วยความจำโปรแกรม: | - |

| ขนาด RAM ข้อมูล: | - |

| แรงดันไฟฟ้าในการทำงาน: | 900 mV ถึง 1.1 V |

| อุณหภูมิในการทำงานต่ำสุด: | - 40 องศาเซลเซียส |

| อุณหภูมิในการทำงานสูงสุด: | + 100 องศาเซลเซียส |

| บรรจุภัณฑ์: | ถาด |

| ยี่ห้อ: | เท็กซัส อินสตรูเมนท์ |

| ความกว้างของบัสข้อมูล: | 8 บิต/16 บิต/32 บิต |

| ประเภทคำสั่ง: | จุดคงที่ / จุดลอยตัว |

| MMACS: | 320,000 MMACS |

| ไวต่อความชื้น: | ใช่ |

| จำนวน I/O: | 16 อินพุต/เอาต์พุต |

| จำนวนตัวจับเวลา/ตัวนับ: | 16 ตัวจับเวลา |

| ประเภทสินค้า: | DSP - ตัวประมวลผลและตัวควบคุมสัญญาณดิจิทัล |

| ปริมาณแพ็คโรงงาน: | 44 |

| หมวดหมู่ย่อย: | โปรเซสเซอร์และคอนโทรลเลอร์แบบฝังตัว |

| แรงดันไฟ - สูงสุด: | 1.1 โวลต์ |

| การจ่ายแรงดัน - ต่ำสุด: | 900 มิลลิโวลต์ |

| หน่วยน้ำหนัก: | 0.252724 ออนซ์ |

♠ ตัวประมวลผลสัญญาณดิจิทัลแบบคงที่และจุดลอยตัวแบบมัลติคอร์

TMS320C6678 DSP เป็น DSP แบบ fixed/floating-point ที่มีประสิทธิภาพสูงสุด ซึ่งใช้สถาปัตยกรรมแบบมัลติคอร์ KeyStone ของ TIด้วยการรวมคอร์ C66x DSP ใหม่และนวัตกรรม อุปกรณ์นี้สามารถทำงานที่ความเร็วคอร์สูงถึง 1.4 GHzสำหรับนักพัฒนาแอปพลิเคชันที่หลากหลาย เช่น ระบบที่มีความสำคัญต่อภารกิจ การถ่ายภาพทางการแพทย์ การทดสอบและระบบอัตโนมัติ และแอปพลิเคชันอื่นๆ ที่ต้องการประสิทธิภาพสูง TMS320C6678 DSP ของ TI นำเสนอ DSP แบบสะสม 11.2 GHz และเปิดใช้งานแพลตฟอร์มที่ประหยัดพลังงานและใช้งานง่าย ใช้.นอกจากนี้ยังสามารถใช้งานร่วมกับ DSP แบบคงที่และแบบทศนิยมในตระกูล C6000 แบบย้อนหลังได้อย่างสมบูรณ์

สถาปัตยกรรม KeyStone ของ TI เป็นแพลตฟอร์มที่ตั้งโปรแกรมได้ซึ่งรวมระบบย่อยต่างๆ (คอร์ C66x, ระบบย่อยหน่วยความจำ, อุปกรณ์ต่อพ่วง และตัวเร่งความเร็ว) และใช้ส่วนประกอบและเทคนิคที่เป็นนวัตกรรมใหม่เพื่อเพิ่มการสื่อสารภายในอุปกรณ์และระหว่างอุปกรณ์ให้สูงสุด ซึ่งช่วยให้ทรัพยากร DSP ต่างๆ ทำงานได้อย่างมีประสิทธิภาพและราบรื่น .ศูนย์กลางของสถาปัตยกรรมนี้คือส่วนประกอบหลัก เช่น Multicore Navigator ที่ช่วยให้การจัดการข้อมูลระหว่างส่วนประกอบต่างๆ ของอุปกรณ์มีประสิทธิภาพTeraNet เป็นแฟบริคสวิตช์แบบไม่ปิดกั้น ช่วยให้สามารถเคลื่อนย้ายข้อมูลภายในได้อย่างรวดเร็วและปราศจากความขัดแย้งตัวควบคุมหน่วยความจำที่ใช้ร่วมกันแบบมัลติคอร์ช่วยให้สามารถเข้าถึงหน่วยความจำที่ใช้ร่วมกันและหน่วยความจำภายนอกได้โดยตรงโดยไม่ต้องใช้ความจุของสวิตช์แฟบริค

• ระบบย่อย TMS320C66x™ DSP Core แปดระบบ (C66x CorePacs) แต่ละระบบมี

– 1.0 GHz, 1.25 GHz หรือ 1.4 GHz C66x แกน CPU คงที่/ลอยตัว

› 44.8 GMAC/Core สำหรับ Fixed Point @ 1.4 GHz

› 22.4 GFLOP/Core สำหรับจุดลอยตัว @ 1.4 GHz

- หน่วยความจำ

› 32K ไบต์ L1P ต่อคอร์

› 32K ไบต์ L1D ต่อคอร์

› 512K Byte Local L2 ต่อคอร์

• ตัวควบคุมหน่วยความจำที่ใช้ร่วมกันแบบมัลติคอร์ (MSMC)

– หน่วยความจำ MSM SRAM ขนาด 4096KB แชร์โดย CorePacs DSP C66x แปดตัว

– หน่วยป้องกันหน่วยความจำสำหรับทั้ง MSM SRAM และ DDR3_EMIF

• เนวิเกเตอร์แบบมัลติคอร์

– คิวฮาร์ดแวร์อเนกประสงค์ 8192 พร้อมตัวจัดการคิว

– DMA ตามแพ็กเก็ตสำหรับการถ่ายโอนค่าโสหุ้ยเป็นศูนย์

• ตัวประมวลผลร่วมของเครือข่าย

– Packet Accelerator เปิดใช้งานการสนับสนุนสำหรับ

› เครื่องบินขนส่ง IPsec, GTP-U, SCTP, PDCP

› L2 User Plane PDCP (RoHC, Air Ciphering)

› ทรูพุตความเร็วสูง 1-Gbps ที่ 1.5 MPPackets ต่อวินาที

– Security Accelerator Engine เปิดใช้งานการสนับสนุนสำหรับ

› IPSec, SRTP, 3GPP, WiMAX Air Interface และความปลอดภัย SSL/TLS

› ECB, CBC, CTR, F8, A5/3, CCM, GCM, HMAC, CMAC, GMAC, AES, DES, 3DES, Kasumi, SNOW 3G, SHA-1, SHA-2 (แฮช 256 บิต), MD5

› ความเร็วการเข้ารหัสสูงสุด 2.8 Gbps

• อุปกรณ์ต่อพ่วง

– สี่เลนของ SRIO 2.1

› 1.24/2.5/3.125/5 GBaud รองรับการทำงานต่อเลน

› รองรับ I/O โดยตรง การส่งผ่านข้อความ

› รองรับสี่ 1 ×, สอง 2 ×, หนึ่ง 4 × และสอง 1 × + หนึ่ง 2 × การกำหนดค่าลิงก์

– PCIe Gen2

› พอร์ตเดียวรองรับ 1 หรือ 2 เลน

› รองรับสูงสุด 5 GBaud ต่อเลน

– ไฮเปอร์ลิงก์

› รองรับการเชื่อมต่อกับอุปกรณ์สถาปัตยกรรม KeyStone อื่นๆ ที่ให้ความสามารถในการปรับขยายทรัพยากร

› รองรับสูงสุด 50 Gbaud

– ระบบย่อยสวิตช์ Gigabit Ethernet (GbE)

› สองพอร์ต SGMII

› รองรับการทำงาน 10/100/1000 Mbps

– อินเทอร์เฟซ DDR3 64 บิต (DDR3-1600)

› พื้นที่หน่วยความจำที่สามารถระบุตำแหน่งได้ 8G ไบต์

– EMIF 16 บิต

– สองพอร์ตอนุกรมโทรคมนาคม (TSIP)

› รองรับ 1024 DS0s ต่อ TSIP

› รองรับ 2/4/8 เลนที่ 32.768/16.384/8.192 Mbps ต่อเลน

- อินเตอร์เฟส UART

– I2

ซี อินเตอร์เฟส

– 16 GPIO พิน

- อินเทอร์เฟซ SPI

– โมดูลสัญญาณ

- ตัวจับเวลา 64 บิตสิบหกตัว

– PLL บนชิปสามตัว

• อุณหภูมิเชิงพาณิชย์:

– 0°C ถึง 85°C

• อุณหภูมิที่ขยาย:

– -40°C ถึง 100°C

• ระบบภารกิจสำคัญ

• ระบบคอมพิวเตอร์ประสิทธิภาพสูง

• การติดต่อสื่อสาร

• เครื่องเสียง

• โครงสร้างพื้นฐานวิดีโอ

• อิมเมจจิ้ง

• การวิเคราะห์

• ระบบเครือข่าย

• การประมวลผลสื่อ

• ระบบอัตโนมัติอุตสาหกรรม

• ระบบอัตโนมัติและการควบคุมกระบวนการ